Analyse de l'A19 Pro : les choix malins d'Apple révélés

Nadim Lefebvre

Nadim Lefebvre- Il y a 5 mois

- 💬 Réagir

- 🔈 Écouter

Alors qu'Apple communique peu sur les détails techniques de ses puces, les analyses approfondies menées par des experts révèlent que la firme de Cupertino ne se contente pas d'améliorer les performances brutes. Avec les A19 et A19 Pro, la marque démontre une maîtrise impressionnante de l'optimisation architecturale, allant bien au-delà des promesses du fondeur TSMC.

Alors qu'Apple communique peu sur les détails techniques de ses puces, les analyses approfondies menées par des experts révèlent que la firme de Cupertino ne se contente pas d'améliorer les performances brutes. Avec les A19 et A19 Pro, la marque démontre une maîtrise impressionnante de l'optimisation architecturale, allant bien au-delà des promesses du fondeur TSMC.

Des gains qui dépassent les attentes

Les chiffres parlent d'eux-mêmes : l'A19 Pro affiche une réduction de taille de 10% par rapport à l'A18 Pro, tandis que l'A19 standard gagne 9% de compacité. Ces résultats interpellent lorsqu'on sait que le passage du processus de gravure N3E vers le N3P de TSMC ne devrait théoriquement apporter qu'environ 4% de gain en densité. Comment expliquer cet écart ? Apple a manifestement développé des stratégies d'optimisation qui vont chercher chaque nanomètre disponible.

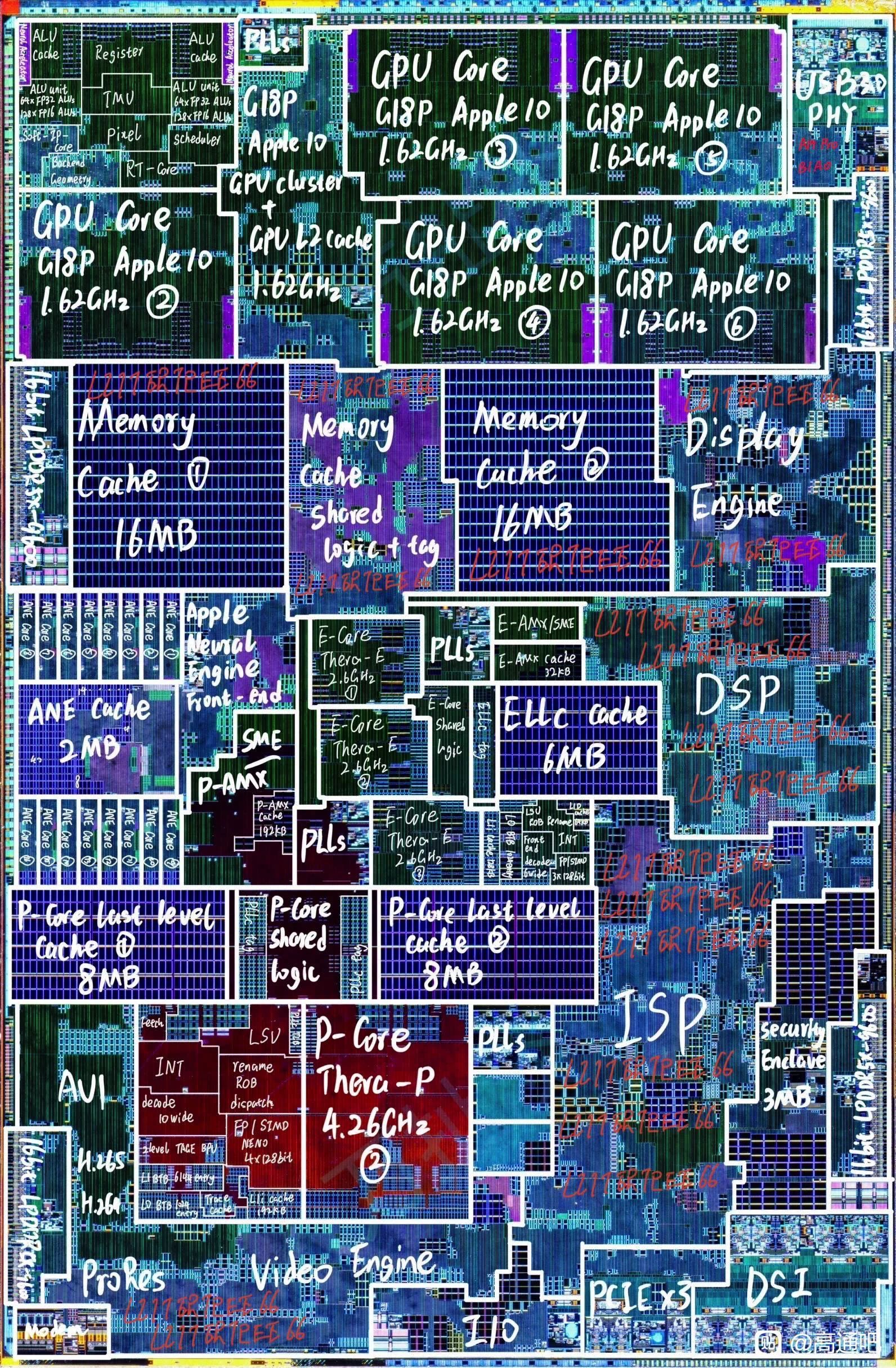

L'analyse détaillée des composants internes révèle des choix architecturaux cohérents avec les performances constatées. Les cœurs haute performance (P-Core) ont été compactés d'environ 4%, pendant que les cœurs basse consommation (E-Core) et le GPU ont gagné 10% de surface. Cette répartition intelligente correspond parfaitement aux orientations prises par Apple : les gains les plus significatifs de cette génération proviennent justement de l'efficacité énergétique et des capacités graphiques. D'ailleurs, Intel prend exactement la même direction sur ses CPU depuis quelques mois.

Une optimisation à tous les niveaux

La mémoire cache, qui occupe traditionnellement une part conséquente de la surface d'une puce, a bénéficié d'une refonte de son organisation. Apple est passé d'une densité de 1,08 mm² pour 4 Mo sur l'A18 à seulement 0,98 mm² sur l'A19, soit une amélioration notable de l'efficacité spatiale. Les blocs secondaires comme le contrôleur d'affichage ou les fonctions de sécurité ont également été revisités pour nécessiter moins de transistors.

Cette approche méthodique présente des avantages concrets en production. Une puce plus compacte permet d'en graver davantage sur chaque wafer, réduisant ainsi le coût unitaire. Le taux de rendement s'améliore également mécaniquement, même si le prix du processus N3P reste plus élevé que le N3E. Cette stratégie contraste avec celle d'autres fabricants qui, lors de transitions similaires, se contentent souvent de conserver la même taille de puce en ajoutant simplement plus de cache.

Apple's iPhone SoC, which are by far the highest volume chip produced on leading edge nodes, just got a significant die shrink while packing in higher performance cores and more cache!

— SemiAnalysis (@SemiAnalysis_) December 11, 2025

A19 Pro is 10% smaller than A18 Pro

A19 is 9% smaller than A18

Looking at core areas, The… https://t.co/Q0bkMUfby1 pic.twitter.com/y4x1sWu5dg